Návštěvnost dne 25. února 2026 byla — 484 927 unikátních návštěvníků !

Návštěvnost dne 26. února 2026 byla — 479 665 unikátních návštěvníků !

Návštěvnost dne 5. března 2026 byla — 475 445 unikátních návštěvníků !

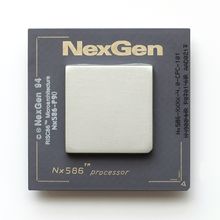

NexGen Nx586

Z Multimediaexpo.cz

NexGen Nx586 je plně 32bitový procesor architektury x86 od firmy NexGen. To znamená, že programy běžící na Nx586 se chovají úplně stejně jako na procesorech Intelu – 486 a Pentium.

Byl to jeden z prvních procesorů pro osobní počítače, který měl dostatečný minimální výkon pro grafické a multimediální aplikace. Zároveň to byl první významnější konkurent procesoru 5. generace – Pentium, který poprvé ukázal, že RISC může být lepší než CISC.

Obsah |

Architektura procesoru

Procesor NexGen Nx586 odlišuje především svou architekturou. Instrukce, načítané z paměti, jsou standardní instrukce 80x86, ale instrukce prováděné v řetězcích procesoru jsou RISCově vyhlížející překlady CISCových instrukcí 80x86. NexGen jim říká instrukce RISC86 a Nx586 je používá pro dosažení výkonu procesorů třídy Pentia.

Pohled NexGenu na Nx586 se významně liší od rozhodnutí Intelu o Pentiu. Nx586 obsahuje tři nezávislé prováděcí jednotky – dvě celočíselné a jednu adresovou, ale neobsahuje jednotku pohyblivé řádové čárky. NexGen říká, že všichni – včetně Intelu – uznávají, že téměř všechen kód 80x86 je celočíselný. NexGen proto věnoval prostor na čipu rozdělené instrukční a datové keši (namísto jednotce pro pohyblivou řádovou čárku), které jsou dvakrát větší než u Pentia, a také integrovanému řadiči cache úrovně 2 (L2). Hardwarovou podporu pohyblivé řádové čárky zajišťuje příbuzný Nx586 – samostatný čip Nx587.

Rychlá vyrovnávací paměť 32 KB na čipu je rozdělena na 16 KB instrukční a 16 KB datové cache. Obě cache byly čtyřcestné a množinově asociativní. Komplexní řadič cache L2 podporuje navíc čtyřcestnou organizaci. Tato relativně velká úroveň množinové asociativity má za následek vyšší poměr zásahů při přístupu do vyrovnávací paměti. Na rozdíl od primární cache je sekundární cache společná.

Řadič L2 cache komunikuje s cache mimo čip přes vyhrazenou sběrnici L2. Tím se odstraní konflikty s externí adresovou a datovou sběrnicí. cache L2 je se zpětným zápisem, zatímco keš L1 je se zápisem skrz. Organizace primární keše se zápisem skrz umožňuje přistupovat k primární i sekundární keši paralelně. V případě nenalezení dat v rámci primární cache je již paralelně téměř dokončen přístup do sekundární cache.

Podpora externí sběrnice, samostatné rozhraní L2 a vyhrazené rozhraní pro FPU znamená, že Nx586 není vývodově kompatibilní s Pentiem. Vyžaduje mnohem větší pouzdro – se 436 vývody oproti 296 u Pentia. Externí sběrnice Nx586 navíc není kompatibilní se sběrnicí Pentia a 486. Nx586 dále vyžadoval zvláštní logiku pro rozhraní se běžnou logikou systémů AT. NexGen dodával čip pro podporu VL-Busu a podporu PCI.

Z CISCu do RISCu

Během zpracování načítá Nx586 CISCové instrukce z instrukční cache a ukládá je v bufferu předvýběru. Tento buffer je rozdělen do tří částí, což Nx586 umožňuje řídit tři různé instrukční proudy najednou. Tím pomáhá udržovat prováděcí řetězce stále plné, když procesor provádí instrukce spekulativně.

Z bufferu předvýběru postupují instrukce do dekodéru/rozdělovače, kde se během každého taktu přeloží jedna ciscová instrukce do jedné nebo více instrukcí RISC86. Na rozdíl od instrukcí CISC implementují instrukce RISC86 čtecí/zápisový model přístupu do paměti. Instrukce RISC86 mají také na rozdíl od ciscových instrukcí s proměnnou délkou délku pevnou. Jsou však podstatně delší než standardní riscové 32-bitové instrukce.

Protože instrukce RISC86 nejsou navrženy pro uložení v paměti, velmi silně se podobají mikrokódu. Hlavní rozdíl je v tom, že nejsou tak perfektně sladěny s hardwarem jako mikrokód. Jsou natolik flexibilní, že mohou pracovat bez modifikací jak s Nx586, tak i s budoucími verzemi této mikroarchitektury, které mohou obsahovat jinou sadu funkčních jednotek. Lze je tedy považovat za určité instrukce mikroarchitektury.

Při procesu dekódování se překládá jedna instrukce CISC během jednoho taktu hodin a jedna nebo více výsledných instrukcí RISC86 se během jednoho taktu odbaví do tří prováděcích jednotek (nebo čtyř, pokud jste si přidali FPU). Nx586 je tedy ze strany CISCu skalárním procesorem, zatímco ze strany RISCu je superskalárním. Hlavním omezením ve vydávání instrukcí je, že během jednoho taktu se může do jedné prováděcí jednotky dostat maximálně jedna instrukce RISC86.

Všechny tři prováděcí jednotky se od sebe liší. Jedna zajišťuje generování adres pro čtení a zápisy, zatímco druhé dvě zpracovávají celočíselné instrukce. První celočíselná jednotka má úplný celočíselný hardware pro násobení a dělení, ale druhá dokáže zpracovávat pouze jednodušší celočíselné instrukce.

Každá prováděcí jednotka, včetně FPU, má před sebou 14-položkovou instrukční frontu. Každá instrukce musí v této frontě strávit aspoň jeden takt, a to i v případě, že je prováděcí jednotka volná. Protože každá instrukce může strávit ve frontě jinou dobu, nemají samotné řetězce pevně určenou hloubku. Nejkratší doba od načtení do vypuštění instrukce trvá sedm taktů.

Protože řetězce mohou být dost dlouhé, věnoval Nx586 hodně prostředků pro minimalizaci podmínek, které by mohly způsobit zablokování nebo vyprázdnění řetězců. Používal dynamické předpovídání větvení a spekulativní provádění, které umožňuje pokračovat v provádění instrukcí ještě před tím, než je znám výsledek podmíněného skoku. Pro obsluhu závislostí dat v řetězcích používal také přejmenovávání registrů a předávání dat.

Nx586 používá 14 přejmenovávacích registrů jako místa určení zápisů do architekturálních registrů 80x86, včetně osmi registrů pro všeobecné použití. Jakmile se instrukce RISC86 vydá z dekodéru/rozdělovače, přiřadí se jí požadované přejmenovávací registry. Teprve až když se instrukce vypouští, je jí dovoleno modifikovat architekturální registry.

Nx586 načítá, dekóduje a překládá instrukce 80x86 a vydává instrukce RISC86 v pořadí daném programem. Instrukce se mohou provádět a dokončovat v jiném pořadí, ale vypouštějí se ve správném pořadí. Dekodér/rozdělovač sleduje vydané instrukce a zajišťuje, aby modifikovaly architekturální registry a spouštěly výjimky v pořadí podle programu.

Velmi výkonná konstrukce Nx586 jasně ukazovala, že mikroarchitektura čipu 80x86 se vůbec nemusí podobat tomu, co nabízí Intel. V řadě běžných benchmarkových testů měl čip srovnatelné výkony jako Pentium.

YouTube

| The first Pentium competitor – NexGen Nx586 |

| NexGen Nx586-P90 Benchmarks |

Externí odkazy

- CPU Museum – NexGen Nx586 (anglicky)

- CPU-collection.de – NexGen Nx586 (anglicky)

- NexGen Nx586-P100 specifications (anglicky)

| Náklady na energie a provoz naší encyklopedie prudce vzrostly. Potřebujeme vaši podporu... Kolik ?? To je na Vás. Náš FIO účet — 2500575897 / 2010 |

|---|